コラム

|

第149回 短期CMOS作製挑戦記

横山 新

|

NMOSトランジスタ回路の実習を2007年より毎年実施していることはコラムNo.121に書いた。その時の受講生の感想文の中に、現在はNMOS回路ではなくCMOS回路が広く使われており、その実習をやって欲しいという声が多数あった。そこで2016年7月から8月にかけて、実習用に設計から製作、測定までを1週間で行えるプロセスを開発した。基本は先のコラムに書いたLOCOS不使用、Alゲート・配線兼用プロセスである。n-wellを形成しさえすれば後は、NMOSとほとんど同じプロセスでできるはずであり、ナノテクプラットフォームの担当教員、研究員と共に早速挑戦した。

1回目は、n-Wellを形成した基板上に2015年と同じプロセスでNMOSを、引き続いてPMOSをトータル3日で作製したが、両者共にゲートリーク電流が大きい不良となった。原因は、(1)NMOSソース/ドレインの砒素インプラ時にイオン電流が大きかったためレジストが炭化してきれいに除去できなかったこと、(2)イオン注入用保護酸化膜をそのままゲート絶縁膜として使用したこと、(3)n-wellを形成する際の高温(1150℃)長時間(9時間)の窒素ガス中での熱処理時に、シリコンが窒化しゲート絶縁不良になったためではないかと考えた。

そこで、2回目の試作(所要日数4日)では、(1)本ゲート酸化の前に犠牲酸化を1回行って不良ゲート絶縁膜を除去した。(2)NMOSのソース/ドレインの砒素インプラ時のイオン電流を50mAから10mAに低減させレジストの炭化を防止した。また、レジストが除去され易い酸素プラズマ処理条件を見出した(2枚以内、30分以上)。(3)インプラ後に保護酸化膜を除去し新たにゲート酸化を行った。(4)その際先のコラムに書いたようにゲート酸化の前後に十分な熱処理を行いソース/ドレイン接合を十分深くした。その結果、NMOS特性は改善されたが歩留りは悪かった。PMOSのソース/ドレインと基板間のリーク電流は依然大きいままであった。

3回目の試作では、(1)NMOSのアクティブ領域エッチングをn-well形成の後にし、(2)n-wellの濃度を3種類振って閾値電圧を調整した。(3)本ゲート酸化の前の犠牲酸化の回数を2回に増やして不良ゲート絶縁膜の完全除去を目指した。(4)砒素インプラの他に燐の熱拡散によってn+領域を作る方法をCMOSに先だってNMOSのみに適用した。その結果、どちらも良好な特性であったため、将来的に微細化に有利な砒素インプラを用いることとした。

その結果、NMOSの特性はほぼ理想的なものになり歩留りも向上した。しかし、依然PMOSのソース/ドレインと基板間のリーク電流は高電圧下では大きいままであった。また、NMOSFETとPMOSFETの閾値電圧はそれぞれ、0.6Vと-0.85Vとアンバランスであった。

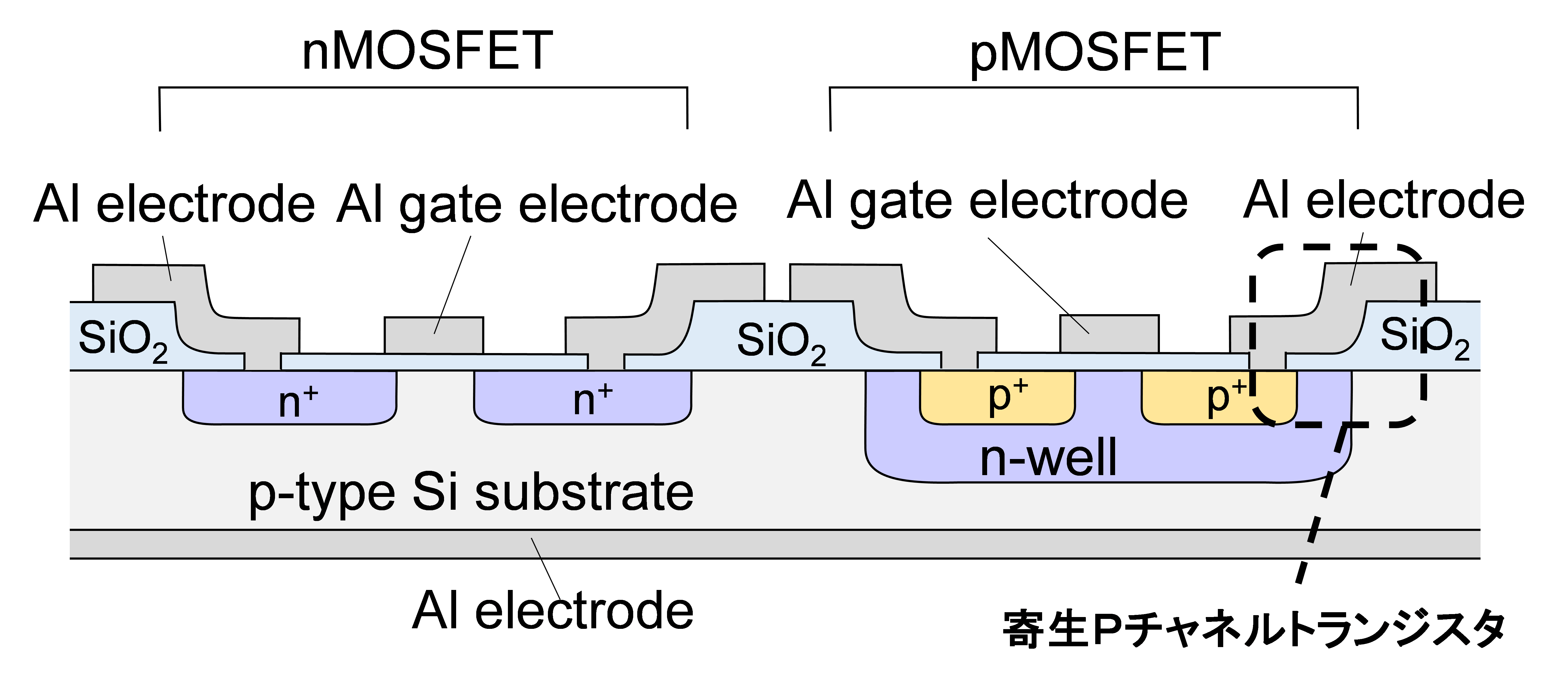

そこで、4回目の試作では、(1)NMOSのチャネルドープ量を増やし、(2)ゲート酸化前後のアニールをそれ以前の950℃から850℃に下げて基板表面のB濃度の減少を防止し閾値電圧の低下防止を図った。その結果、それぞれの閾値電圧は0.9Vと-0.85Vとほぼバランス良くできた。しかし、依然PMOSのソース/ドレインと基板間のリーク電流はドレイン電圧の絶対値が2.5V以上で増大する結果となった。その特性はどのデバイスでも同じであった。そこで、構造上の問題があると疑った。添付完成図の点線内を見ると、そこに寄生PMOSトランジスタが形成されていて、その閾値電圧を計算してみると-2.5Vであることが分かった。寄生トランジスタの基板表面に砒素インプラでn+層を作ることでこの問題は解決できる。電源電圧2.5V以下ではリークの問題もなく、インバータ、リングオシレータなどが良い特性で動作している。

どの失敗も後になって落ち着いて考えてみれば、ごく当たり前のことであるが、期限が決まっている実際の製作現場ではすぐには気付かなかった。「失敗は成功のもと」という諺通りではあるが、失敗にめげず、何度も挑戦する勇気と体力が重要である。

その後2017年度の8月初旬に同様な実習を開催し、スリランカモラトゥワ大学の学生5名を含む18名の参加があった。2日で設計し、n-wellまで完成したウェハを用いて3日でCMOSを作製し、残りの2日で測定を行った。上記PMOSFETの寄生ランジスタによるリークを低減させるために、新たにPMOSFET用のフィールド酸化膜を形成した。しきい値電圧の絶対値はp,nチャネル共に1.09Vと非常にバランス良くできた。今後は、市販では得られないCMOSと他のデバイス(センサー、MEMSや光集積回路)を組み合わせた独自性のある集積回路を開発していく予定である。